## Digital LLRF feedback control system for the J-PARC linac

Shinichiro Michizono<sup>1,A)</sup>, Zhigao Fang<sup>A)</sup>, Seiya Yamaguchi<sup>A)</sup>, Shozo Anami <sup>A)</sup>,

Hiyoyuki Suzuki<sup>B)</sup>, Tetsuya Kobayashi<sup>B)</sup>

A) High Energy Accelerator Research Organization (KEK)

1-1 Oho, Tsukuba, Ibaraki, 305-0801

B) Japan Atomic Energy Research Institute (JAERI)

2-4, Shirakata-Shirane, Tokai, Naka, Ibaraki, 319-1195

#### Abstract

Twenty high power klystrons will be installed in the J-PARC linac. The rf fields are required to be stable less than +1% in amplitude and +-1deg. in phase. The digital feedback (FB) system using FPGAs are adopted so as to satisfy these requirements. External monitors using wave-detectors and mixers are utilized for confirming the stability. The measured stabilities are less than +-0.15% in amplitude and +-0.15 deg. in phase during the  $500\mu$ s flat-top. A tuner control system was tested and 18-hour FB operation was also carried out.

# J-PARC線形加速器での高周波デジタルフィードバック制御

## 1.はじめに

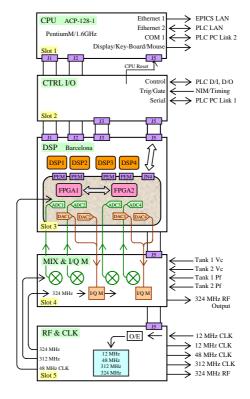

J-PARC陽子リニアックでは、20台のクライスト ロン (324MHz、最大3MW)が使用され、RFQ,3台 のDTL,16台のSDTLモジュールを励振する[1,2]。高 周波源に対しては、振幅・位相について±1%、±1 度の精度の安定度を要求されており、この仕様を満 たすために、FPGAを用いた高速デジタルフィード バック(FB)システムを採用した[3,4]。システムはコ ンパクトPCI(cPCI)筐体に収納される。図1のシス テムの模式図に示すようにFPGAボードには4個のADC と4個のDACおよび2個のFPGA VirtexII2000)が搭 載されている。空洞内と空洞入力信号がMix&I/Qモ ジュールで中間周波数(12MHz)に変換され、ADCに 直接入力される。空洞内信号(ADC1およびADC2)に ついてはFPGA1に取り込まれ、IQ成分に分離した上 で設定値と比較してPI制御の計算を行い、フィード フォワード(FF)信号を足して、DACからIQ変調器 に出力される。空洞入力信号はADC3およびADC4に入 力され、空洞内信号との位相差から空洞離調を算出 するために利用される。

今回は2台のSDTL空洞からなるSDTLモジュールに対して、ベクターサム試験、および外部モニタでの安定性評価、チューナー制御試験、ランニング試験を行った。

#### 2.試験結果

#### 2.1 ベクターサムコントロール

SDTLモジュールでは、1台の高周波源により2台のSDTL空洞を励振する。この場合は2空洞の電界の和が一定となるような制御(ベクターサム制御)を

図1 コンパクトPCI(cPCI)の構成

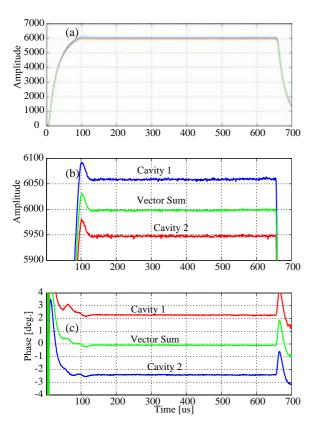

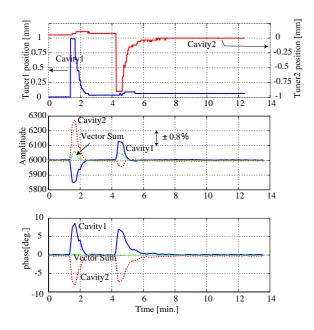

行う。ベクターサムを行ったときのFBループ内のモニタ(FBモニタ)波形を図2に示す。設定は現在のところFPGAで処理する整数値をそのまま使用しており、振幅の設定範囲は0から8192である。設定波形はフラット部分についてI成分が6000、Q成分が0(振幅6000、位相0度に相当)であり、立ち上がり部分はQ

-147-

<sup>&</sup>lt;sup>1</sup> E-mail: Shinichiro.MICHIZONO@kek.jp

図2 FBモニタでの波形。(a):振幅、(b):振幅(拡大)、(c):位相。振幅、位相の設定値6,000と0度である。比例ゲインは4、積分ゲインは0.01。

値が30,000に相当する形状で行っている。ベクターサムのパルス内フラット部分は振幅・位相について、±0.06%、±0.05度以内の安定度である。

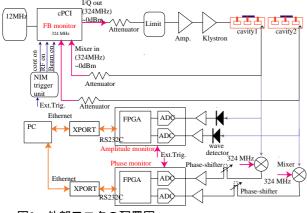

## 2.2 外部モニタ

これまで空洞内の電界強度については、FBを行っているFPGAボードで得られた値(FBモニタ)を示してきたが、FBの安定性を評価するためにFBループ外部での計測を行った。図3に示すように空洞信号を2系統に分岐して、振幅・位相をそれぞれ検波器とミキサーを使って測定した。検波器出力とミキサー出

図3 外部モニタの配置図

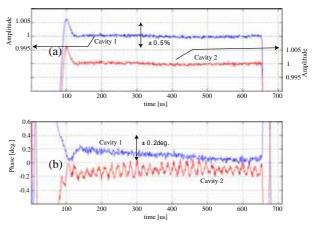

図4 外部モニタでのパルス内安定度。(a):振幅(規格化したもの)、(b)位相。振幅、位相の設定値は図2と同じく6,000と0度である。

力は、増幅器で増幅した後に14ビットアナログデジタル変換器(ADC)に入力する。ADCではデータを1μ秒おきに取り込んでおり、データはホストのコンピュータに保存される[5]。得られた波形を図4に示す。検波器、位相出力共に校正後の値に変換してある。パルス内の振幅および位相安定度はそれぞれ±0.2%、±0.2度以内となっている。空洞内では、波形に示されている様な速い成分は存在せず(Q値20,000の場合の周波数の半値幅は16kHz程度)、実際の安定度はこれより高くなる。FBのパラメータは変化させず設定値のみを6000,5000,4000とした場合のパルス内の安定度を表1にまとめる。数10%の振幅の変化に対してもFBが安定であることを確認できた。

#### 2.3 チューナー制御

空洞内電界と空洞入力信号の位相差は、空洞の離調と関係する。空洞が運転周波数と一致した時を基準位相差として、空洞内と空洞入力の位相差(測定位相差)と基準位相差の差から空洞の離調を計算できる。空洞の離調が設定した離調(ビーム負荷がある時は空洞を少し離調した場合に最も効率的な運転が可能となる。)を大きく外れた場合(たとえば1度)、cPCI上のDSPボードから空洞チューナーを調整する。調整により、測定離調と設定離調の差が十分小さくなった(たとえば0.2度)場合にチュー

表1 設定振幅と安定度 (500 µ sのフラット部分)

|   | Michigan Company |       |       |       |

|---|------------------|-------|-------|-------|

|   | 設定振幅             | 4000  | 5000  | 6000  |

| 忑 | FBモニタ (振幅)[%]    | ± .10 | ± .08 | ± .06 |

| 洞 | FBモニタ ( 位相 ) [度] | ± .07 | ± .08 | ± .05 |

| 1 | 検波器振幅モニタ[%]      | ± .16 | ± .17 | ± .12 |

|   | Mixer位相モニタ[度]    | ± .12 | ± .15 | ± .14 |

| 忑 | FBモニタ (振幅)[%]    | ± .09 | ± .09 | ± .08 |

| 洞 | FBモニタ ( 位相 ) [度] | ± .07 | ± .08 | ± .06 |

| 2 | 検波器振幅モニタ[%]      | ± .18 | ± .15 | ± .12 |

|   | Mixer位相モニタ[度]    | ± .18 | ± .17 | ± .16 |

| サ | FBモニタ (振幅)[%]    | ± .07 | ± .06 | ± .06 |

| ム | FBモニタ ( 位相 ) [度] | ± .05 | ± .04 | ± .05 |

図5 チューナー制御試験時のチューナー位置とFB モニタの時間変化。

ナー制御を休止する。実際にチューナー制御を行った場合のFBモニタの時間変化を示す。図中の約1分後に空洞1を+1mm動かし、また、約4分後に空洞2を-1mm動かしている(チューナーを1mm変化させると15度程度の離調が生じる。)。この値は、実機で想定している値(数度程度)より大きいが、動作確認のために行っている。空洞離調が変化している

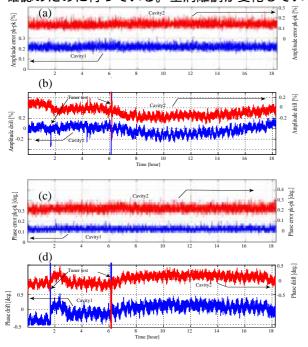

図6 ランニング試験時の外部モニタの時間変化。(a):フラットトップの振幅の幅(最大値と最小値の差)、(b):フラットトップの振幅平均値の時間変化、(c):フラットトップの位相の幅、(d):フラットトップの位相平均値の時間変化。

間も、FBモニタではベクターサムが一定となっている。また、2分程度でチューナー制御がうまく動作することが確かめられた。

#### 2.4 ランニング試験

FBの安定度を見るために18時間程度の連続運転を行った。このときの外部モニタでの振幅・位相の時間を図6に示す。ここでは、振幅・位相のフラット部分の最大・最小値の差(図5(a),(c))およびフラット部分の平均値の時間変化(ドリフト、図5(b),(d))を示している。パルス内の振幅・位相は $\pm 0.15\%$ (0.3%pk-pk)、 $\pm 0.15$ 度(0.3gpk-pk)程度で、また、短時間のパルス間の振幅・位相の変化も $\pm 0.1\%$ 、 $\pm 0.15$ 度程度に収まっている。

現在のFBシステムではRF&CLKボードとMixerボードが外気温変化により出力位相が変化することがわかっている(外気温1度で位相1度程度)。これについてはボードの改版作業中であり、外気温1度の変化で位相変化が0.1度以下となるものが試作できている。今回の測定でドリフトが0.3度程度現れているのは外気温が0.5度程度変化しているためである。

#### 3.まとめ

SDTLモジュールを使ってデジタルフィードバック系の安定度測定を行った。検波器とミキサーを使った外部モニタ系も使用し、パルス内安定度が±0.15%、±0.15度以下であることを確認した。また、チューナー制御試験も行い、水温変化や入力の高周波電力の変化で空洞の離調が変化した場合もチューナーを正しく制御することを確かめた。18時間程度のランニング試験を行い、安定度を測定した。パルス内の振幅・位相安定度はランニング運転中±0.15%、±0.15度以下を維持し、パルス間の変動を含めても、全体として±1%、±1度の仕様を十分満たすことを確認できた。

#### 参考文献

- [1] S.Anami, et al., "J-PARC Linac Low Level RF Control", Proceedings of the 1st Annual Meeting of Particle Accelerator Society of Japan and the 29th Linear Accelerator Meeting in Japan, Aug. 4-6, 2004, Funabashi, Japan.

- [2] S.Anami, et al., "Automatic Recovery Control of J-PARC Linac RF Sources", in this meeting.

- [3] S.Michizono et al., "Digital feedback system for J-PARC linac RF source", Proceedingsof the 22<sup>nd</sup> international Linear Accelerator Conference (LINAC 2004), Luebeck, Germany, August 16-20, 2004, KEK Preprint 2004-77.

- [4] E. Chishiro, et al., "Status of the RF system for J-PARC Linac", in this meeting.

- [5] H.Katagiri, et al., "Microwave measurements and control using the FPGA board", in this meeting.